Analog Devices (ADI) has unveiled This new platform consists of a small family of reference designs, starting with the and the

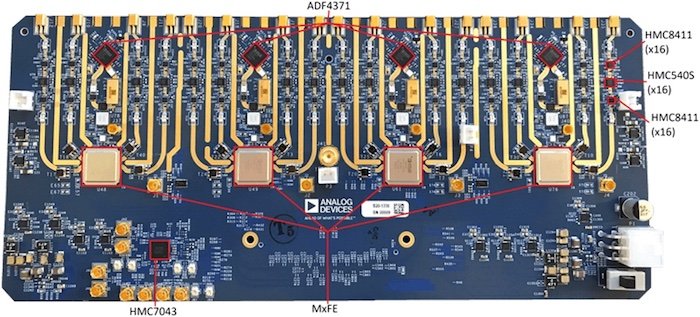

The new 16TX/16RX quad mixed (digital/analog) radio front end. Image used courtesy of

The Quad-MxFE platform is available as a complete reference design, including an RF signal chain, software architectures and application samples, and the power design architecture. The calibration board, which is also available, is programmable with MATLAB.

MATLAB algorithms allow users to confirm channelization metrics such as combined channel dynamic range, phase noise measurements, and most importantly, phase determinism.

According to Analog Devices, this platform may be especially useful in aerospace and defense applications ranging from phased-array radars to SATCOM (satellite communications) on the ground.

ADI’s Quad-MxFE Specifications

At its core, this new from ADI is a synchronized array of multiple analog-to-digital (ADCs) and digital-to-analog converter (DACs). The platform comes in two quad-array offerings, with the or the chipsets, which have 4D4A or 4D2A converters, respectively.

Quad-MxFE's block diagram. Image used courtesy of

Eight serializer/deserializers () interface with a (separate optional platform) operating at upwards of 24.75 Gbps/lane () or 15.5 Gbps/lane () to move digital data into and out of each of the four chips on the platform.

Beamforming Technology Basics

Beamforming technology has seen massive investment over the past several years, with the military investing significant resources in phased-array technology. Applications can utilize both conventional RF and (radar detection and characterization).

Commercially, with the optimization of MIMO antenna systems.

Fundamentally, beamforming operates by introducing analog and digital delays into a coherent signal chain. These delays steer the direction of the aggregate main lobe propagating from the antenna superstructure.

A phased array receiver with time delays used in beam-steering. Image used courtesy of

The propagated signals will add constructively (and destructively) to generate (or receive) a wavefront in the direction of interest and suppress unwanted side lobes in the antenna pattern.

This procedure can be complicated, requiring strict timing constraints on the digitizer array. Each digitizer module's phase must be deterministically quantified with respect to the other modules of the array to generate coherent and useful wavefronts.

ADI tackles this complexity at the sub-system with multi-chip calibration algorithms and system-level with the calibration board.

Multi-chip Synchronization Calibration and Phase Determinism

Electronically steering an antenna pattern using a phased array requires knowing each array element's relationship (phase). —just that they be quantified so that software adjustment can be performed to align them.

The AD9081/AD9082 can synchronize each digitizer chip in the complete system by reprogramming DSP blocks such as:

- Numerically controlled oscillators (NCOs)

- Programming finite impulse response blocks for phase and amplitude

A schematic of the multi-chip calibration between baseband FPGA and the MxFE platform. Image used courtesy of

In the sub-assembly, two procedures are completed: NCO master-slave sync and a one-shot sync, which is used to prepare the array for the NCO master-slave sync. These procedures bring the system one step closer to phase determinism by aligning specific inputs.

After those two procedures are completed, the phase-locked loops on the Quad-MxFE are calibrated for thermal drift with the calibration board.

Calibration board (left) interfaced to MxFE board (middle) and Xilinx Virtex FPGA (right). Image used courtesy of

ADI says its new reference design will help simplify prototyping and proliferation of advanced phased-array communication technology, especially for military, aerospace, and commercial applications.

Do you work with phased-array applications for telecommunications? What aspect interests you the most about this new mixed RF design? Let us know in the comments below.